УДК 621.382

## ЭНЕРГОНЕЗАВИСИМЫЕ АСИНХРОННЫЕ РЕГИСТРЫ НА ОСНОВЕ МЕМРИСТОРОВ ДЛЯ НИЗКОПОТРЕБЛЯЮЩИХ ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ

### <sup>1</sup>Ковалев А.В., <sup>1</sup>Малюков С.П., <sup>2</sup>Пермяков Н.В.

<sup>1</sup>ФГАОУ ВПО «Южный федеральный университет», Ростов-на-Дону, e-mail: andr@fep.tti.sfedu.ru; <sup>2</sup>ФГБОУ ВПО «Санкт-Петербургский государственный электротехнический университет «ЛЭТИ» им. В.И. Ульянова (Ленина)», Санкт-Петербург, e-mail: andr@fep.tti.sfedu.ru

Описывается реализация энергонезависимого асинхронного регистра, который использует наноразмерные мемристоры в качестве элемента памяти при отключении питания (намеренном или случайном). Показана возможность тесной интеграции мемристоров с КМОП-схемами, отличающейся от традиционного подхода использования энергонезависимой памяти в виде отдельного относительно крупного, медленного и «монолитного» блока на нижнем уровне проектной иерархии. Моделирование и анализ подтвердили успешную работу схемы хранения состояния регистра и его восстановления. Полученные результаты показывают, что интеграция цифровых асинхронных логических устройств и мемристоров может открыть путь для разработки и применения энергонезависимых вычислительных приложений на малых аппаратных платформах, которые работают от нестабильных или часто отключаемых источников энергии. Предложенный в данной статье подход объединения достоинств асинхронных схем и мемристоров позволит создавать низкопотребляющие приложения для различных мобильных, носимых или просто эксплуатирующихся в жестких полевых условиях электронных устройств. А также сохранять и обрабатывать ценные данные, получаемые, например, массивом сенсорных элементов, питающихся от альтернативного источника энергии с нестабильными периодами генерации – солнечной панели или ветроустановки.

Ключевые слова: мемристоры, асинхронные схемы, энергонезависимость

# NONVOLATILE ASYNCHRONOUS REGISTERS BASED ON MEMRISTORS FOR LOW-POWER COMPUTING SYSTEMS

### <sup>1</sup>Kovalev A.V., <sup>1</sup>Malukov S.P., <sup>2</sup>Permyakov N.V.

<sup>1</sup>Southern Federal University, Rostov-on-Don, e-mail: andr@fep.tti.sfedu.ru; <sup>2</sup>Saint-Petersburg State Electrotechnical University «LETI», St. Petersburg, e-mail: andr@fep.tti.sfedu.ru

The paper describes the implementation of an asynchronous nonvolatile register that uses nanoscale memristors as storage elements when power is turned off (either intentionally or accidentally). This suggests the possibility of integration with CMOS circuits and memristors. This differs from the traditional approach of using non-volatile memory as a single separate large, slow and «monolithic» block on the lower level of design hierarchy. Modeling and analysis confirmed the successful operation of the register circuit – state was storaged and restored from it. These results indicate that the integration of asynchronous digital logic devices and the memristors could open the way for the development and application of non-volatile computing applications for small hardware platforms that operate on unstable or accidentally disconnected sources of energy. The proposed approach combining the advantages of asynchronous circuits and memristors will create low-power applications for various mobile, portable or simply operating electronic devices in harsh environment. And also to maintain and process valuable information obtained, for example, an array of sensor elements, fed from an alternative source of energy from unstable periods of generation – solar panels or wind turbines.

Keywords: memristors, asynchronous circuits, non-volatility

Мемристорные устройства, обладающие возможностью динамического изменения проводимости в зависимости от предыдущих состояний и режимов протекания тока, могут быть использованы как элементы энергонезависимой памяти для хранения конфигурации в программируемых логических интегральных схемах или для «замораживания» данных вычислений при отключении питания [10].

В работе [8] описан подход к интеграции мемристоров с синхронными триггерами КМОП-схем, при котором мемристоры как отдельные элементы энергонезависимой памяти разбросаны по всей схеме (при каждом триггере). В данном подходе, в частности, не учитывается внезапное (непланируемое) отключение питания, а также то, что в таких

синхронных схемах дополнительно потребуется управление тактированием триггеров при возникновении необходимости записать состояние в мемристорный элемент. Построение электронных устройств на базе асинхронной логики дает значительный выигрыш по энергоэффективности [1, 2, 3].

В большинстве вычислительных систем электропитание отключается или теряется время от времени. Во время потери мощности большая часть данных, хранящаяся в энергозависимых схемах, может быть сохранена в энергонезависимой памяти, а затем восстановлена, когда возобновляется подача тока.

Для основных традиционных технологий энергонезависимой памяти операция сохранения относительно медленная (десятки или сотни микросекунд для Flash) в срав-

нении с записью на жёсткий диск (единицы миллисекунд). Неожиданное отключение питания (по разным причинам: кончился заряд аккумулятора, прервался питающий контакт при вибрации, прекратил генерировать достаточно тока альтернативный источник энергии и т.п.) во время записи или обработки данных может привести к их потере.

Описана концепция [9, 10, 11] и экспериментальная демонстрация [15] интеграции наноразмерных мемристорных элементов с КМОП-схемами, при которой мемристоры располагаются над каждым триггером вычислительных блоков и соответственно практически не требуют дополнительной площади кристалла, т.е. энергонезависимая память может быть неразрывно вплетена в вычислительную структуру, а не располагать отдельным относительно медленным блоком.

В частности, это тесная интеграция может дать экономичные, миниатюрные однокристальные платформы, которые могут сохранять свое состояние за один такт для применения в портативных устройствах с прерывистым источником энергии.

В этой статье представляется схема энергонезависимого асинхронного регистра, которая основывается на мемристорном устройстве в качестве элемента энергонезависимой памяти для гибридных кристаллов КМОП/мемристоры.

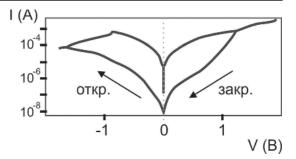

На рис. 1 показаны циклы переключения мемристора между открытым и закрытым состояниями.

Рис. 1. Вольт-амперная характеристика мемристора из [12] (ось тока в логарифмическом масштабе)

## 1. Энергонезависимая схема асинхронного регистра

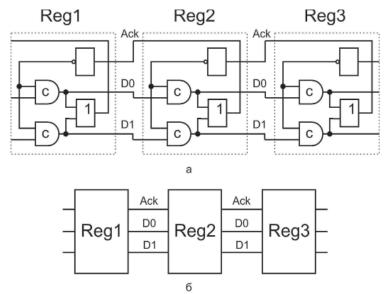

Асинхронные двухпроводные регистры-защелки [7] позволяют сохранять и передавать биты данных (бит представлен двумя проводниками D0 и D1) при одновременном контроле корректности состояний входящих информационных сигналов, т.е. такой регистр определяет факт поступления данных и генерирует сигнал подтверждения (Ack) этого события. Такое поведение является независимым от задержек и обеспечивает надежную работу. На рис. 2 показан пример объединения асинхронных двухпроводных регистров-защелок в единый конвейер, независимый от задержек поступления данных. На рисунке в схеме используется С-элемент Маллера [5].

Рис. 2. Асинхронный сдвиговый регистр из двухпроводных четырехфазных регистров-защелок: а – внутренняя схема с С-элементами; б – абстрактный вид

Элемент ИЛИ на рис. 2 объединяет выходы С-элементов и генерирует сигнал подтверждения для предыдущего каскада, говорящий о том, что данные получены и за-

фиксированы. Вход подтверждения Ack, принимающий сигнал со следующего каскада, управляет приемом новой порции входных данных в отдельно взятом регистре-защелке.

Подобный конвейер FIFO (First In First Out) использован для апробации подхода к интеграции асинхронных схем и мемристоров в качестве распределенной энергонезависимой памяти. При этом стоит учесть, что в упомянутом выше методе из [8] отключения

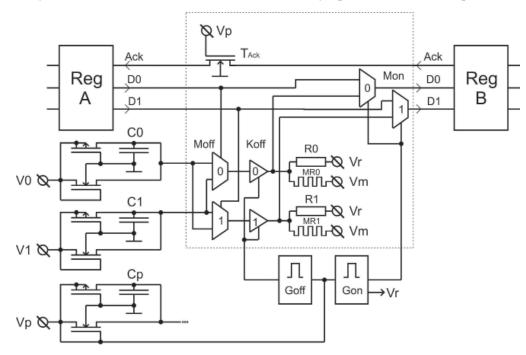

питания должны быть кем-то инициированы, и соответственно должно оставаться время (как минимум 1–2 тактовых периода или время переключения мемристора) на запись информации в мемристоры, предлагаемая схема такого устройства показана на рис. 3.

Рис. 3. Схема запоминания состояний асинхронных регистров

На рис. 3 отображена структура, запоминающая состояния двух проводников, представляющих один информационный бит. Поскольку упомянутый асинхронный конвейер работает по четырехфазному протоколу, то по двум информационным проводникам регистра передается не два, а три состояния: «1», «0» и «нет данных». По этой причине для их запоминания нельзя обойтись только одним мемристором.

Для записи состояния в мемристор часто требуется прикладывать к его выводам напряжение, отличное от общего питающего и используемого в остальной схеме. С этой целью предусмотрены терминалы V1 и V0, которые служат для записи состояний «1» и «0» в мемристоры, соответственно. Напряжение на втором выводе мемристоров Vm, как правило, равно 0 В.

Терминал Vp – для общего питающего напряжения всей схемы (кроме мемристоров). Сигнал Vr служит для управления записью и чтением состояний мемристоров. Его формирует блок Gon, который выдает один импульс необходимого напряжения Vr сразу после включения питания на вспомогательный резистор для чтения состояний мемристоров.

В предложенной схеме (см. рис. 3) в левой части присутствуют конденсаторы (Ср,

С0 и С1), которые предназначены для поддержания уровней питающих напряжений в течение времени записи в мемристоры (10 нс и менее) сразу после внезапного отключения питания. Между конденсаторами и терминалами подключения питания вставлено по паре транзисторов, составляющих проходной ключ, который находится в открытом состоянии, если питание присутствует, и переходит в закрытое, когда питание исчезает. Это сделано с целью нейтрализовать внутреннее сопротивление «севшего» аккумулятора, батареи или обмотки генератора при разряде соответствующего конденсатора, т.е. разряд Ср, С0 и С1 сразу после исчезновения внешнего питания будет происходить практически полностью через полезную схему.

Емкость конденсаторов может быть определена на основе заданных исходных параметров общей потребляющей схемы: мощности и напряжения питания.

Динамика разряда конденсатора будет происходить по формуле:

$$U_C = U_0 e^{-\frac{iW}{U^2 C}},\tag{1}$$

где  $U_{\rm C}$  – текущее напряжение на конденсаторе;  $U_{\rm 0}$  – начальное напряжение; t – текущее

время с начала разряда; W — потребляемая мощность схемы; U — напряжение питания схемы; C — емкость конденсатора.

Таким образом, после преобразований (1), время разряда до конкретного уровня напряжения можно определить так:

$$T_C = -\frac{\ln\left(\frac{U_C}{U}\right)U^2C}{W}.$$

(2)

Время, необходимое для записи состояний в мемристоры, как уже упоминалось, должно быть около 10 нс. В нашем случае, для надежности примем его равным 20 нс. Также для питания схемы на период записи

состояний в мемристоры зададим необходимое напряжение, которое отличается от питающего в нормальном режиме не более чем на 2%. Другими словами, в период записи напряжение при разряде должно снизиться до уровня 98%.

Подставив указанные числовые значения в (2), получим требуемую емкость:

$$C = -\frac{2 \cdot 10^8 W}{\ln\left(\frac{49}{50}\right) U^2}.$$

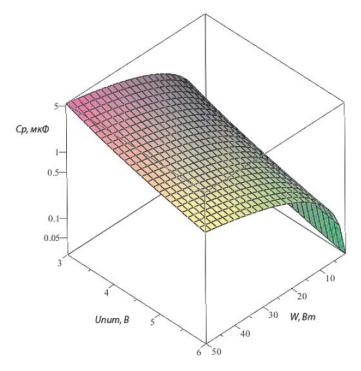

На рис. 4 показана поверхность, определяемая последним выражением.

Рис. 4. Зависимость требуемой емкости конденсатора от напряжения питания (U) и потребляемой мощности схемы (W). Вертикальная шкала в логарифмическом масштабе

Как можно видеть на диаграмме (рис. 4), для схем с малым потреблением (порядка 1 Вт) и питанием, например, 5 В, необходимая емкость начинается с 30–40 нФ.

Роль мемристоров в схеме на рис. 3 следующая: при внезапном отключении питания закрываются проходные ключи и начинается разряд конденсаторов, т.е. поддержание работоспособного уровня напряжения. Одновременно с этим блок Goff генерирует один прямоугольный импульс длиной 10–20 нс, который открывает ключи, пропускающие напряжение записи непосредственно на мемристоры. Величина напряжения записи зависит от состояния проводников (D0, D1) двухпроводного информационного выхода левого регистра

(Reg A), т.е. D0 и D1 управляют мультиплексорами напряжений V0 и V1.

В момент возобновления питания блок Gon генерирует один прямоугольный импульс, переключающий мультиплексоры на мемристоры. Длины импульса должно хватить на считывания состояния с делителя напряжения (мемристор и вспомогательный резистор) и запись уровня в правый регистр (Reg B).

Блокирующий транзистор (TAck) на сигнале Ack предохраняет от передачи подтверждения регистру Reg A во время записи его состояний в мемристоры.

После подачи питания схема работает в обычном режиме асинхронного конвейера. При этом мультиплексоры Mon\_0

и Mon\_1 переключены на проводники D0 и D1, а состояние Moff\_0 и Moff\_1 не имеет значения, т.к. проходные ключи ( $K_0$ ,  $K_1$ ) закрыты.

Если напряжение, снимаемое с делителя напряжения, недостаточно для записи состояния в регистр, то следует добавить в схему пороговый элемент (компаратор) для выделения четкого сигнала.

#### 2. Моделирование

Для реализации мемристоров могут быть использованы различные материалы, в том числе материалы с изменением фазы [6, 14], оксиды металлов [4, 13] и др. Эти

материалы различаются по свойствам, например, по скорости переключения состояний мемристора.

Для моделирования в работе использованы мемристоры на основе диоксида титана (хорошая совместимость с КМОП-процессами), размерами 50×50 нм², время переключения менее 10 нс, время хранения состояния более 1 года, высокий уровень выхода годных [12].

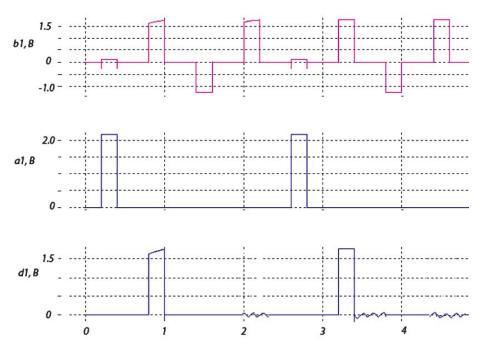

На основе созданной SPICE-модели мемристора проведено смешанное цифро-аналоговое моделирование. На рис. 5 показан фрагмент временной диаграммы режимов записи и чтения состояний мемристоров.

Рис. 5. Диаграммы записи и чтения состояний мемристоров

Предложенная схема позволяет избежать статического потребления мощности мемристорами, т.к. ток в них во время операционной (нормальной) работы практически отсутствует (Vm = 0, Vr = 0, а выход ключей — в третьем состоянии).

Последовательность событий, заданная при моделировании: включение питания, установка бита «1» в регистр Reg A, выключение питания и запись состояния в мемристор, включение питания и чтение состояния из мемристора, запись этого состояния в регистр Reg B, далее повторение той же последовательности для бита «0».

Для повышения числа безошибочных циклов, как правило, увеличивают ширину подходящих к мемристорам проводников и/или используют низкорезистивные материалы.

#### Выводы

В статье показано, что мемристор может использоваться в качестве элементов памяти в энергонезависимой схеме асинхронных регистров. Подобные схемы могут быть использованы для построения «энергонезависимых» процессоров, т.е. для функциональных блоков, у которых логическое состояние может быть сохранено за очень короткое время, что позволяет создавать вычислительные системы, питающиеся от нестабильных (прерывистых во времени) источников энергии, таких, как ветрогенераторы, солнечные батареи, приливные генераторы и т.п.

Работа выполнена при финансовой поддержке Министерства образования и науки Российской Федерации (гос. соглашение №14.А18.21.0107) в рамках ФЦП «Научные и научно-педагогические кадры инновационной России» на 2009—2013 годы.

#### Список литературы

- 1. Ковалев А.В. Метод проектирования быстродействующих асинхронных цифровых устройств с малым энергопотреблением // Известия вузов. Электроника. 2009. № 1. с. 48–53.

- 2. Ковалев А.В. Технологии энергосбережения в микроэлектронных устройствах: монография. Таганрог: Издво ТТИ ЮФУ, 2009. 100 с.

- 3. Brej C., Garside J.D. A Quasi-Delay-Insensitive Method to Overcome Transistor Variation // In Proceedings of the 18th International Conference on VLSI Design held jointly with 4th International Conference on Embedded Systems Design (VLSID '05). IEEE Computer Society, Washington, DC, USA, 2005. P. 368–373.

- 4. Gibbons J F and BeadleW E 1964 Switching properties of thin NiO films Solid-State Electron. 7 785–90.

- 5. Muller D.E. and Bartky W.S. A Theory of Asynchronous Circuits // Proceedings of an Interantional Symposium on the Theory of Switching, Cambridge, MA: Harvard Univer. Press, 1959. P. 204–243.

- Ovshinsky S R 1968 Reversible electrical switching phenomena in disordered structures Phys. Rev. Lett. 21 1450–3.

- 7. Principles of asynchronous circuit design A systems perspective / J. Sparsø and S. Furber (eds). Kluwer Academic Publishers, 2001 (ISBN 0-7923-7613-7).

- 8. Robinett W., Pickett M., Borghetti J., Xia Q.F., Snider G.S., Medeiros-Ribeiro G. and Williams R.S.A memristor-based nonvolatile latch circuit // Nanotechnology NANOTECHNOL. 2010. vol. 21, no. 23. 235203.

- 9. Snider G S and Williams R S 2007 Nano/CMOS architectures using a field-programmable nanowire interconnect Nanotechnology 18 035204.

- 10. Strukov D.B., Snider G.S., Stewart D.R. and Williams R.S. 2008 The missing memristor found Nature 453 80–3.

- 11. Strukov D.B. and Likharev K.K. 2005 CMOL FPGA: a reconfigurable architecture for hybrid digital circuits with two-terminal nanodevices Nanotechnology 16 888–900.

- 12. Strukov Dmitri B., Borghetti Julien L., Yang J. Joshua, Snider Gregory S., Stewart Duncan R., Williams R. Stanley Switching dynamics in titanium dioxide memristive devices // Journal of Applied Physics; Oct 2009, Vol. 106 Issue 7, pp. 074508 074508-6.

- 13. Waser R., Dittmann R., Staikov G. and Szot K. 2009 Redox-based resistive switching memories—nanoionic mechanisms, prospects, and challenges Adv. Mater. 21 2632–63.

- 14. Wuttig M and Yamada N 2007 Phase-change materials for rewriteable data storage Nat. Mater. 6 824–32.

- 15. Xia Q et al 2009 Memristor/CMOS hybrid integrated circuits for reconfigurable logic Nano Lett. 9 3640–5.

#### References

1. Kovalev A.V. A method of designing high-speed asynchronous digital devices with low-power consumption // Izvesti-ya Vuzov. Electronics. no. 1, 2009. pp. 48–53.

- 2. Kovalev A.V. Energy saving technologies in microelectronic devices. Monograph./ Taganrog: TIT SFU Publisher, 2009. 100 p.

- 3. Brej C., Garside J.D. A Quasi-Delay-Insensitive Method to Overcome Transistor Variation // In Proceedings of the 18th International Conference on VLSI Design held jointly with 4th International Conference on Embedded Systems Design (VLSID '05). IEEE Computer Society, Washington, DC, USA, 2005. pp. 368–373.

- 4. Gibbons J F and BeadleW E 1964 Switching properties of thin NiO films Solid-State Electron. 7 785–90.

- 5. Muller D.E. and Bartky W.S. A Theory of Asynchronous Circuits // Proceedings of an Interantional Symposium on the Theory of Switching, Cambridge, MA: Harvard Univer. Press, 1959. pp. 204–243.

- 6. Ovshinsky S R 1968 Reversible electrical switching phenomena in disordered structures Phys. Rev. Lett. 21 1450–3.

- 7. Principles of asynchronous circuit design A systems perspective / J. Sparsø and S. Furber (eds). Kluwer Academic Publishers, 2001 (ISBN 0-7923-7613-7).

- 8. Robinett W., Pickett M., Borghetti J., Xia Q.F., Snider G.S., Medeiros-Ribeiro G. and Williams R.S. A memristorbased nonvolatile latch circuit // Nanotechnology NANO-TECHNOL, vol. 21, no. 23, 235203, 2010.

- 9. Snider G.S. and Williams R.S. 2007 Nano/CMOS architectures using a field-programmable nanowire interconnect Nanotechnology 18 035204.

- 10. Strukov D.B., Snider G.S., Stewart D.R. and Williams R.S. 2008 The missing memristor found Nature 453 80–3.

- 11. Strukov D.B. and Likharev K.K. 2005 CMOL FPGA: a reconfigurable architecture for hybrid digital circuits with two-terminal nanodevices Nanotechnology 16 888–900.

- 12. Strukov Dmitri B., Borghetti Julien L., Yang J. Joshua, Snider Gregory S., Stewart Duncan R., Williams R. Stanley Switching dynamics in titanium dioxide memristive devices // Journal of Applied Physics; Oct 2009, Vol. 106 Issue 7, pp. 074508 074508-6.

- 13. Waser R., Dittmann R., Staikov G. and Szot K. 2009 Redox-based resistive switching memories—nanoionic mechanisms, prospects, and challenges Adv. Mater. 21 2632–63.

- 14. Wuttig M. and Yamada N. 2007 Phase-change materials for rewriteable data storage Nat. Mater. 6 824–32.

- 15. Xia Q. et al 2009 Memristor/CMOS hybrid integrated circuits for reconfigurable logic Nano Lett. 9 3640–5.

#### Рецензенты:

Агеев О.А., д.т.н., профессор, директор Научно-образовательного центра «Нанотехнологии» Южного федерального университета, г. Таганрог;

Рындин Е.А., д.т.н., профессор, ведущий научный сотрудник Южного научного центра Российской академии наук (ЮНЦ РАН), г. Ростов-на-Дону.

Работа поступила в редакцию 16.10.2012.